読み方 : フリップフロップかいろ

フリップフロップ回路【flip-flop circuit】

概要

フリップフロップ回路とは、最も基本的な構造の論理回路の一つで、二つの状態のいずれかを保持することができるもの。“flip-flop”とは「パタパタ」あるいは「ぎったんばっこん」に相当する擬音語で、出力値が入れ替わる様子をシーソーに例えたものとされる。

現在の入力と共に過去の入力も利用する順序回路の一種で、二つの状態を「0」および「1」に対応付け、1ビットの値を保持する記憶回路として利用される。通電が途絶えると状態が失われる揮発性の素子であり、永続的なデータ保存などには使えない。

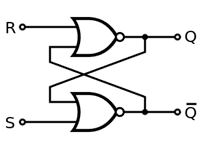

最も有名な「RSフリップフロップ」は、R(Reset:リセット)とS(Set:セット)の二つの入力、QとQの二つの出力で構成される。内部はRとSのそれぞれにNOR回路、あるいはNOT回路とNAND回路の組み合わせが接続されており、それぞれ相手方の出力とRあるいはSが入力となり、出力がQとQとなる。

RとSの入力を(0,1)にするとQとQの出力は(0,1)、(1,0)としたときは(1,0)となり、QとQは必ず逆の値となる。入力がいずれも0のときは前回変更されたときの状態を維持するため、記憶素子として利用することができる。出力を変化させたいときだけR、Sに値をセットする。

フリップフロップ回路を大量に並べてメモリ装置としたものをSRAM(Static RAM:スタティックRAM)と呼び、DRAMに比べてリフレッシュ動作が不要で高速に動作するという利点がある。CPU内部でデータを保持するレジスタやキャッシュメモリなどにも応用されている。回路構成により、RS型以外にも「JKフリップフロップ」、「Dフリップフロップ」(D:Delay)、「Tフリップフロップ」(T:Toggle)などの種類がある。

(2023.3.12更新)

「フリップフロップ回路」の関連用語

他の用語辞典による「フリップフロップ回路」の解説 (外部サイト)

資格試験などの「フリップフロップ回路」の出題履歴

▼ 基本情報技術者試験

【令3修1 問21】 メモリセルにフリップフロップ回路を利用したものはどれか。

【令1修7 問23】 二つの安定状態をもつ順序回路はどれか。

【平31春 問21】 メモリセルにフリップフロップ回路を利用したものはどれか。

【平30修1 問22】 図の論理回路において,S=1,R=1,X=0,Y=1のとき,Sを一旦0にした後,再び1に戻した。この操作を行った後のX,Yの値はどれか。

【平29修12 問22】 メモリセルにフリップフロップ回路を利用したものはどれか。

【平28秋 問22】 メモリセルにフリップフロップ回路を利用したものはどれか。

【平28修7 問21】 図の論理回路において,S=1,R=1,X=0,Y=1のとき,Sを一旦0にした後,再び1に戻した。この操作を行った後のX,Yの値はどれか。

【平27修12 問21】 二つの安定状態をもつ順序回路はどれか。

【平27修6 問22】 メモリセルにフリップフロップ回路を利用したものはどれか。

【平26秋 問22】 二つの安定状態をもつ順序回路はどれか。

【平26春 問20】 メモリセルにフリップフロップ回路を利用したものはどれか。

【平24秋 問23】 二つの安定状態をもつ順序回路はどれか。

【平22春 問25】 二つの安定状態をもつ回路で,SRAMの記憶セルに使用される順序回路の基本構成要素はどれか。

【平22修1 問25】 図の回路において出力が x=0,y=1 である状態から,x=1,y=0 に変える入力a及びbの組合せはどれか。![]() 。

。

【平21修6 問23】 フリップフロップ回路を利用した高速なメモリはどれか。