読み方 : ぜんかさんき

全加算器【full adder】フルアダー/全加算回路

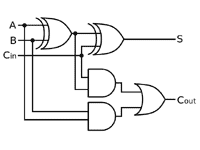

加算を行う回路を加算器というが、全加算器は2つのビット列の同じ桁の値と、隣の下位桁からの繰り上がりを加算し、その桁の加算後の値と、上位桁への繰り上がりの有無を表す「キャリー」(carry out)の2つを出力する。キャリー出力は繰り上がりがなければ「0」、あれば「1」となる。

加算する3つの値の「0」と「1」の組み合わせにより「00」から「11」までの8種類の和が得られるが、下位ビットがその桁の値として、上位ビットが上位桁へのキャリーとして出力される。キャリーは隣の上位桁の全加算器に入力される。

一方、下位桁からの繰り上がりを考慮せず、単純に2つの値の和を求める回路を「半加算器」(half adder:ハーフアダー)という。繰り上がりのない最下位桁の和を求めるのに使われる。全加算器は半加算器2つとOR回路1つを組み合わせて構成することができる。

最下位桁に半加算器を置き、各桁についての全加算器を桁の数だけ並べて連結すると、複数桁の2進数の加算を行う論理回路を構成することができる。例えば、半加算器1つと全加算器7つを並べれば8ビットの全加算器となる。

(2023.8.22更新)

「全加算器」の関連用語

他の用語辞典による「全加算器」の解説 (外部サイト)

資格試験などの「全加算器」の出題履歴

▼ 基本情報技術者試験

【令4修6 問22】 図に示す全加算器の入力xに1,yに0,zに1を入力したとき,出力となるc(けた上げ数),s(和)の値の組合せとして,正しいものはどれか。

【平29修1 問21】 図は全加算器を表す論理回路である。図中のxに1,yに0,zに1を入力したとき,出力となるc(桁上げ数),s(和)の値の組合せとして,正しいものはどれか。

【平27修7 問22】 図に示す全加算器の入力xに1,yに0,zに1を入力したとき,出力となるc(けた上げ数),s(和)の値の組合せとして,正しいものはどれか。

【平26修1 問27】 図は全加算器を表す論理回路である。図中のxに1,yに0,zに1を入力したとき,出力となるc(桁上げ数),s(和)の値の組合せとして,正しいものはどれか。

【平22修12 問28】 図は全加算器を表す論理回路である。図中のxに1,yに0,zに1を入力したとき,出力となるc(桁上げ数),s(和)の値の組合せとして,正しいものはどれか。

【平21秋 問25】 図に示す全加算器の入力xに1,yに0,zに1を入力したとき,出力となるc(けた上げ数),s(和)の値の組合せとして,正しいものはどれか。