読み方 : はんかさんき

半加算器【half adder】ハーフアダー/半加算回路

加算を行う回路を加算器というが、半加算器は2つのビット列の同じ桁の値同士を加算し、その桁の加算後の値と、上位桁への繰り上がりの有無を表す「キャリー」(carry out)の2つを出力する。キャリー出力は繰り上がりがなければ「0」、あれば「1」となる。

2つのビットが両方「0」ならその桁の値として「0」(0+0=0)を、片方が「1」なら「1」(0+1=1, 1+0=0)を出力するが、両方「1」ならば結果は「10」(1+1=10)と2桁の値になるため、その桁の値として「0」を、キャリーとして「1」を出力する。キャリーは隣の上位桁の全加算器に入力される。

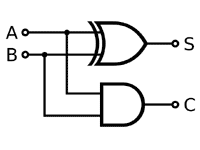

半加算器は基本的な論理回路の組み合わせで構成でき、AND回路2つ、OR回路1つ、NOT回路1つで作ることができる。XOR回路が利用可能であれば、XOR回路1つとAND回路1つで構成することもできる。

半加算器は下の桁からの繰り上がりを考慮しないため、そのままでは最下位桁の加算にしか使えない。下の桁からの繰り上がりを入力として受け付けるものは「全加算器」(full adder:フルアダー)と呼ばれ、2つの半加算器とOR回路により構成することができる。最下位桁以外の加算には全加算器が用いられる。

(2023.8.22更新)

「半加算器」の関連用語

他の用語辞典による「半加算器」の解説 (外部サイト)

資格試験などの「半加算器」の出題履歴

▼ 基本情報技術者試験

【令3修1 問22】 図に示す,1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平29春 問22】 図に示す,1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平28修6 問23】 図に示す構造の論理回路は,どの回路か。![]() 。

。

【平28修1 問22】 図に示す1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平26修7 問22】 図に示す構造の論理回路は,どの回路か。![]() 。

。

【平26修6 問23】 図に示す1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平24修7 問27】 図に示す1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平23春 問25】 図に示す,1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。

【平22修6 問28】 図に示す構造の論理回路は,どの回路か。![]() 。

。

【平21春 問25】 図に示す1桁の2進数xとyを加算して,z(和の1桁目)及び c(桁上げ)を出力する半加算器において,AとBの素子の組合せとして,適切なものはどれか。